In This Article

What is Direct Memory Access (DMA)?

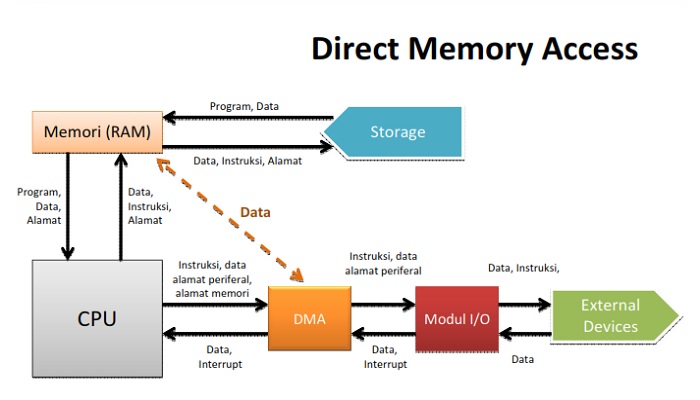

Direct Memory Access or DMA in short, refers to a hardware controlled technique of transferring data from the Random Access Memory or RAM of the computer to any other parts of it without the CPU processing it.

This method also involves the input/output device to directly transmit or receive data from the memory of the system or an external hardware to access the memory without the intervention of the CPU.

KEY TAKEAWAYS

- The main objective of the DMA process is to enhance the performance of the computer without increasing the workload of the CPU.

- Data is moved in this process by using memory to memory copying technique and the DMA is configured in different ways such as single-bus detached DMA, single-bus integrated DMA and I/O bus.

- DMA provides different types of services and operations such as resource control, organizing DMA objects and retrieving attributes based on resources allocated.

- There are different DMA techniques followed to improve the performance of the processor such as Bus Master DMA, Scatter/Gather DMA, and Common Buffer System DMA.

Understanding Direct Memory Access (DMA)

The Direct Memory Address controls the data and information transfer between the memory, the processor, and the I/O devices.

It reduces the load on the processor, which typically has to control a wide variety of operations in a computer.

The DMA controller speeds up the process and improves the performance of the computer.

The Direct Memory Access typically uses memory to memory copying while moving data within the memory and there are different ways in which the configuration of the DMA can be made. These are:

- Single-bus, detached DMA – In the single-bus, detached DMA the same system bus is shared by all its modules which makes it act as a surrogate processor. This DMA uses programmed I/O for transferring data through the module between the I/O module and the memory. This configuration is pretty cheap but is also quite inefficient because two bus cycles are used for every word transfer.

- Single-bus, integrated DMA – In this particular configuration, there is a conduit between one or more I/O modules and the DMA module which does not consist of the system bus. The number of bus cycles needed is reduced substantially because the DMA logic can be an element of the I/O module or there can be a distinct module to control one or more I/O modules. The DMA module uses the system bus shared by the DMA module with the memory and CPU for exchanging data with the memory and that with the I/O modules typically happen off the system bus.

- I/O bus – In this configuration, which is further improved, have the I/O modules connected to the DMA module with the I/O bus. This reduces the number of I/O interfaces needed in the DMA module. In fact, there is only one interface required to exchange data with the memory. This system bus is shared by the memory and the CPU and the data exchange between the DMA module and the I/O modules happens off the system bus.

There are different aspects of Direct Memory Access that can be best described by the numerous abstractions used in the DDI/DKI. These are:

- DMA object – This refers to the source or destination memory of a DMA transfer

- DMA handle – This refers to the returned opaque object that is used in succeeding DMA subroutine calls for referring to the DMA objects and

- DMA cookie – This refers to a contiguous and entirely addressable part of a DMA object and consists of the DMA addressing information necessary for programming the DMA engine.

The drivers of the device typically allocate Direct Memory Access resources for the object and then the DMA routines carry out any execution that is specific to that platform.

The driver then receives the DMA handle so that it can find out the DMA resources that are allocated for the object. The driver saves this handle and passes it during ensuing calls to DMA routines. However, this should not be interpreted in any way.

Services and Software

There are different services provided by the Direct Memory Access handle that can define the operations such as:

- Controlling DMA resources

- Orchestrating the DMA objects and

- Reclaiming attributes with respect to the allocated resources.

There are different software components that facilitate Direct Memory Access.

For example, the DMA handle is used by the several calls to DMA routines to figure out the allocated DMA resources to an object, as said earlier.

An object represented by it is covered fully by one or more DMA cookies which is also a continuous part of memory to or from which data is transferred by the DMA engine.

The information available in a Direct Memory Access attribute provided by the driver is used by the system to determine how exactly an object needs to be divided into several cookies.

The object may be even broken into several Direct Memory Access windows if it is too large to fit the request considering the system resource restrictions.

Each window has the necessary resources allocated when each of them is activated at a time and may contain one or more than one cookie.

However, there may be a few specific Direct Memory Access engines that may accept multiple cookies.

These engines can typically perform Scatter-Gather I/O without needing any help from the system.

It is only then that the device can be programmed to reallocate the entire amount of bytes that are covered by all these Direct Memory Access cookies collectively.

Direct Memory Access Controller

The most important component that facilitates Direct Memory Access is the DMA controller.

This particular unit provides the interface between the I/O devices and the bus.

The DMA controller is initiated by the processor of the system by sending specific information such as:

- The starting address

- The number of words to transfer in a data block and

- The direction of transfer of data, whether it is from the I/O devices to the main memory or the other way around.

In order to work or make the data transfer, the DMA controller needs to share the bus with the processor.

The Bus Master holds this bus at a given time.

The processor stops executing the current program to stop using this bus when a transfer is to be made, augments the program counter, and shifts data over the stack.

It then sends a select signal to the DMA controller via the address bus.

The DMA controller can have more than one external device connected to it and can also contain several other register units such as:

- The address unit register to generate addresses and select the I/O device for data transfer

- The control unit register to control the direction of data transfer and

- The data count register to keep count of the number of data blocks transferred.

When the DMA controller is free, a bus request signal is sent to have control over the bus.

The processor grants it and the DMA controller now becomes the Bus Master.

It can now interact with I/O devices and memory directly without the need of the CPU.

When the data transfer is completed, the bus request signal is disabled by it and the bus control is handed over to the CPU once again.

The same process follows when an I/O device wants to make a data transfer.

There are three specific modes in which the DMA transfers are made.

These are:

- Burst Mode – In this mode the buses are handed over to the CPU by the DMA controller only after a data transfer operation is completed fully. This is why this mode is also referred to as Block Transfer Mode. In this case the CPU has to wait till the bus is handed over to it, even if it has a few priority tasks on hold.

- Cycle Stealing Mode – In this mode the control of the buses are handed over by the DMA controller to the CPU after every byte. There are bus signal requests made continually by the DMA controller to the CPU in this process. This way, the CPU does not have to wait for a long time till the bus is free and handed over to it. However, this mode is not as fast as the burst mode.

- Transparent Mode – In this mode, data transfer is made only when the CPU does not need the bus to execute any specific instructions. This is the slowest mode of all but is quite efficient to improve the overall performance of the system since the CPU can function uninterruptedly and the DMA transfers are free with reference to time. However, the hardware must find out when the processor does not need the bus, which is quite complicated. This process is also referred to as the ‘Hidden DMA data transfer mode.’

These DMA controllers are used in sound cards, graphics cards, network cards, and others as well as in multi-core processors for an intra-chip transfer.

Direct Memory Access Techniques

There are different Direct Memory Access programming techniques followed. Some of these include:

- Scatter/Gather DMA

- Common Buffer System DMA

- Bus Master DMA

All these DMA techniques help in improving the activity and performance of the processor as well as the I/O transfer rate and each of them follow different routines.

The Scatter/Gather DMA use a general sequence of support routines for its operations such as:

- MmGetMdlVirtualAddress to get required index in the MDL which is a specific factor in the call to GetScatterGatherList

- GetScatterGatherList when the device driver needs the Bus Master adapter or the DMA controller of the system being ready to program Direct Memory Access

- PutScatterGatherList when the data requested is transferred or when there is a device I/O error resulting in the driver failing the IRP.

In this particular DMA, for the first routine, a pointer to the MDL at Irp->MdlAddress and for the two other routines an adapter object pointer returned by IoGetDmaAdapter are necessary parameters.

As for the Common Buffer System DMA, the driver follows common sequence of support routines such as:

- RtlMoveMemory at the discretion of the driver writer to copy and transfer data from a locked-down user buffer to the common buffer allocated by the driver

- AllocateAdapterChannel when the device driver needs the system DMA controller being ready to program it for Direct Memory Access

- MapTransfer with the MDL that defines the common buffer allocated by the driver in order to set up the DMA controller for the data transfer operation

- FlushAdapterBuffers when the DMA transfer is completed by the driver to or from the secondary device and

- FreeAdapterChannel when the data requested is transferred or when there is a device I/O error resulting in the driver failing the IRP.

Once again, the adapter object pointer is the necessary parameter returned by IoGetDmaAdapter to all of the above support routines except the first one.

And finally, as for the Bus Master DMA, the devices need the following support from the system:

- Packet-based DMA when the adapter lets the driver decide when a DMA transfer operation should be done or when to start another operation for any given IRP and

- Common-buffer DMA or continuous DMA when the adapter does not let the driver decide when a DMA transfer operation should begin or be completed or even when a single buffer region is utilized repeatedly and constantly for DMA transfers.

However, according to the nature of the Bus Master adapter it will be decided whether the driver will use one of the two supports mentioned above, or is it required to use them both.

Direct Memory Access Buffering

The processor typically comes with a dedicated memory on chip. This chip acts as the read or write buffer for the I/O with the external memory.

The buffers typically reside in the data memory on a DSP and the buffering is managed with intelligence.

Typically, there are two buffers for every Direct Memory Access channel that are dedicated for reading and there are two other buffers for writing external memory.

Each of the buffers in both these sets are referred to as the current buffer and the previous buffer.

If the read buffer is full, an interrupt is sent by the DMA controller to inform the CPU.

The operating system may also notify it. It is after this that the roles of current and present buffer are switched.

On the other hand, when the data present in the current write buffer is written to the external memory, the CPU is also notified once again by the DMA controller.

This buffering by the Direct Memory Access helps the CPU to work with the previous read or write buffers and the DMA can continue working with the current read or write buffers.

Ideally, it is the dma-buf subsystem that helps in buffer sharing and synchronization by providing a framework that helps in sharing buffers during hardware access across different subsystems and device drivers.

In addition to that, it also helps in synchronizing the asynchronous hardware access.

On the other hand, the shared Direct Memory Access buffers act as an ‘exporter’ or an ‘importer’ buffer while buffer sharing by a device driver.

For example, if a device driver A wants to use the buffers of device B then A is called the user or importer buffer and B is called the exporter buffer.

Both the exporter and importer buffers serve different functions.

For example, as for the export buffer it:

- Manages or implements operations in struct dma_buf_ops

- Allows sharing the buffer by other users by using dma_buf sharing APIs

- Manages the details of buffer allotment, wrapped int a struct dma_buf

- Determines the tangible backing storage where such allocation occurs and

- Takes care of the migration of the scatter list for all the shared users of the particular buffer.

And, as for the user or importer buffer, it helps one of the several sharing buffer users. It does not need to care for the allocation of the buffer or where it is allocated.

It simply helps by meeting the need for a mechanism to access the scatter list.

This makes up the buffer in memory which is mapped to its own address space which helps in accessing the same area of the memory.

How Does It Work?

As for the standard Direct Memory Access, which is also referred to as third-party DMA, it uses a DMA controller to work.

This controller produces memory addresses and initiates memory read and write cycles.

Apart from that, it also covers several hardware registers that the CPU can read or write.

These registers typically consist of different elements such as:

- A byte count register

- A memory address register and

- One or more control registers.

The functions of these registers also help in the working process of the Direct Memory Access and depend on the features provided by the DMA controller.

The control registers in particular can assign a combination of controls which includes:

- The source

- The destination

- The size of the transfer block

- The number of bytes to transfer in a single burst and

- The direction transfer while reading from or writing to the I/O devices.

On the other hand, the host process contributes to the working process of the Direct Memory Access with its input, output, and memory to memory operations.

This processor typically initializes the DMA controller with the amount of words to transfer as well as the memory address to use. Apart from that, it also instructs the peripheral device to start the data transfer.

After that, the DMA controller offers the read/write control lines along with the addresses to the system memory.

Until an entire data block is completely transferred, the DMA controller increases its internal address register every time a byte of data is geared up for a transfer between the memory and the peripheral device.

The Direct Memory Access also sends specific instructions such as:

- The read or write operations

- The number of words to read or write

- The starting location and

- The address of the input-output device.

The DMA uses the read and write control lines and the data lines to communicate these instructions.

After that, while the CPU continues to do the other important jobs, the DMA module transfers the whole block of data to or from the memory directly bypassing the CPU.

And, when the transfer operation is completed, the DMA module informs the CPU by sending an interrupt signal to it that it is done with using the system bus.

The entire mode of operation is completed in three different modes as applicable such as:

- The burst mode

- The cycle stealing mode and

- The transparent mode.

All these modes are explained before.

The DMA controller also plays its significant role in the working process of the Direct Memory Access as already explained earlier.

Why is Direct Memory Access Used?

Direct Memory Access is primarily used to move large blocks of data which other data transferring modes such as programmed I/O and Interrupt Driven I/O modes of data transfer fails.

It is the DMA controller that completes such tasks most effectively and at a much faster rate.

The DMA can move the data between the RAM or Random Access Memory of the system and the block storage on the Solid State Drives or the hard disks or even the storage area network controllers.

When there is a need to read or write data by a process, a request is made to the Direct Memory Access which signals it when the data is in the place it needs to be.

Ideally, the Direct Memory Access performs some basic operations when the CPU wants to read or send a block of data.

For example, it issues instructions specifically to the DMA module with some particular information that includes:

- The read or write information that are sent through read and write control lines

- The number of words to be written or read that is stored in the data count register and are exchanged through the data lines

- The starting location in the memory to read from or write to that is stored in the address register and communicated through the data lines and

- The address of the I/O device used in the operation which is communicated through the data lines.

In short, the DMA is designed to optimize the performance of the devices at and being dedicated for such tasks.

It can move data faster and much better than the Central Processing Unit which has typically got a lot of other things to do.

What Does Direct Memory Access Do?

Direct Memory Access actually transfers data on its own without the need of the CPU.

The primary use of it is to transfer data to and from the I/O devices with the help of a distinct DMA controller that informs the DSP processor when it is ready to make a transfer.

Therefore, the DMA controller that manages the operation while sending data from a peripheral to the motherboard directly without using the microprocessor, increases the over operation of the system.

This is because the CPU is relieved from the hassles of copying each piece of data by means of a peripheral bus from the input/output device and can perform other tasks till the specific operation is completed.

What are the Types of Direct Memory Access?

There are usually three major types of Direct Memory Accesses that a device may work, each of which has unique characteristics and functionality.

- Bus Master DMA – In these types of devices, which acts like a real bus master, the Direct Memory Access engine is located on the board of the device and the driver programs the DMA registers of the device directly. The transfer count and address are given to the devices which are usually acquired from the DMA cookie.

- Third Party DMA – This type of DMA uses the system DMA engine that resides on the main system board. There are many DMA channels offered for use by these devices for transferring data between the memory and the device. The drivers use the routines of the DMA engine needed for programming and initializing the DMA engine. During every data transfer, the DMA engine is programmed by the driver which then gives the command to the device to initiate the data transfer with the help of the engine.

- First Party DMA – In these types of devices, the device itself drives the Direct Memory Access bus cycles by using a channel from the DMA engine of the system. This particular channel is configured by using a function in a cascade mode. This prevents the DMA engine from interfering with data transfer.

In addition to that, you will also find some other host platform Direct Memory Access types.

These platforms offer the devices either of these two types of memory access:

- Direct Memory Access and

- Direct Virtual Memory Access or DVMA.

When the platform supports DMA, the device is provided with a physical address by the system in order to perform DMA object transfers.

This transfer, in this case, may contain a number of physically separate transfers actually such as when an application moves a buffer that spans quite a few contiguous virtual pages that map to the physically discontiguous pages.

To handle this disconnected memory, such devices usually come with a type of Scatter-Gather DMA ability.

Characteristically, the IA systems offer physical addresses for direct transfer of memory.

On the other hand, for the systems that support DVMA, they have a virtual address for making transfers.

In such situations, some sort of MMU or Memory Management Unit is provided to the device by the underlying platform.

This actually converts access to the virtual addresses by the device into the appropriate physical addresses.

Transfer is made to and from a virtual contiguous image by the device that can be mapped to discontiguous physical pages.

These devices typically do not need to have Scatter-Gather DMA ability.

Usually, it is the SPARC platforms that provide virtual addresses for direct transfer of memory.

What are the Benefits of Direct Memory Access?

There are lots of benefits of using Direct Memory Access in your computer. A few of them are:

- It allows reading from or writing to the memory by a peripheral device without needing using the processor and

- It enables faster processing due to lower clock cycles since the peripheral devices populate memory and the CPU can do other necessary jobs.

However, there are a few downsides of using a Direct Memory Access as well, just as it is in any other product. The most significant of them all are:

- Its dependence on the DMA controller to execute the operations

- The higher cost of the system due to the use of DMA controllers and

- The cache coherence issues.

How Can Direct Memory Access Improve System Performance?

Direct Memory Access helps the external devices in transferring information to and from the memory of the computer directly without the need of using the processor at all.

This improves the overall performance of the system.

This is because the Direct Memory Access controller does all of the necessary jobs once it is set up.

The transfer happens in the background which leaves the processor free so that it can do other necessary jobs.

Proceeding at its own rate, the Direct Memory Access can deal effectively with the speed and volume of data coming in.

The CPU would not need to keep a check on it continuously as it would have required if it was a programmed IO.

This would have resulted in a colossal waste of resources.

How to Enable or Disable Direct Memory Access?

You can enable or disable Direct Memory Access in different ways depending on the operating system loaded in your computer.

Here are a few general and specific ways to go ahead with it.

You may use the BIOS or Basic Input Output System setup to enable Direct Memory Access in your computer system.

Simply enter the BIOS setup and look for the option, though the exact location of the DMA option may vary according to the BIOS and the motherboard.

Usually, you will find this option in the ‘Advanced’ or ‘Chipset’ section. Enable it and save the changes before exiting BIOS.

You may also use a software utility program if there is no Direct Memory Access option in the BIOS.

Windows operating systems typically come with a common utility called the ‘Device Manager.’

The process to follow in this case includes:

- Clicking on the Start menu

- Typing ‘Device Manager’ in the search box

- Looking for the device you want to enable the Direct Memory Access in from the list of all devices that you have installed in your computer as shown in the Device Manager

- Double-clicking on it

- Opening the Properties window

- Clicking on the ‘Details’ tab

- Finding the DMA setting

- Setting it to ‘Enabled’

- Saving the changes made and

- Closing the Device Manager window.

You may need to restart your computer once you are done with the settings so that the changes take effect.

Sometimes, the default Direct Memory Access cannot be used due to incorrect installation or any system error.

In order to enable or disable the DMA in this case, the processes you need to follow include:

- Signing in as an administrator into the computer

- Clicking on Start button

- Clicking on Control Panel when the Start menu expands

- Clicking on Hardware and Sounds in the Control Panel Windows which is usually located on the left pane

- Clicking on Hardware and Sounds

- Finding ‘Devices and Printer’ under it

- Clicking on ‘Device Manager’ option

- Double clicking on the ‘IDE ATA/ATAPI controllers’ option shown in the list device connected to your computer in the Device Manager window

- Opening its Properties of IDE ATA/ATAPI controller

- Right clicking on the properties to open the particular channel

- Clicking on ‘Advance Settings’ tab there

- Clicking on the ‘Enable DMA’ checkbox or un-ticking and ‘Enable DMA’ option to enable or disable Direct Memory Access respectively and

- Clicking on OK.

In order to enable or disable Direct Memory Access feature if you are using Window 7 operating system, the process is almost the same and involves:

- Logging into your computer as an administrator

- Clicking on Start button

- Clicking on Control Panel

- Clicking on System and Security in the Control Panel window

- Clicking on Device Manager under System

- Double clicking on IDE ATA/ATAPI controllers and following the next steps as mentioned above.

If you are using a Windows 95, 98, or ME system, the processes to follow are:

- Going to Start menu

- Selecting Settings

- Clicking on Control Panel

- Double clicking on the System icon

- Clicking on the Device Manager tab

- Clicking on the ‘+’ sign located alongside the device you want to change

- Selecting the device you want to change

- Clicking on the Properties button

- Clicking on the Settings tab

- Selecting or deselecting the DMA checkbox and

- Clicking OK.

And, if you are using a Windows 2000 or XP system and want to enable or disable the Direct Memory Access option, the processes to follow are:

- Visiting the Start menu

- Selecting Settings

- Selecting Control Panel

- Clicking on the System icon

- Clicking on the Hardware tab

- Clicking on the Device Manager button

- Selecting IDE ATA/ATAPI Controllers

- Right clicking on the Primary IDE Channel icon

- Selecting Properties

- Clicking on Advanced Settings tab

- Enabling or disabling DMA from the menu that drops down and

- Clicking OK.

So, check the operating system you are using in your computer and follow the appropriate steps.

Conclusion

After knowing the basic and more-than-the-basic aspects of Direct Memory Access through this article, you now know how important a technology it is today.

Now you know how it can improve the overall performance of the computer by a significant margin if you enable it to get the most out of it.