In This Article

What is MIPS Architecture?

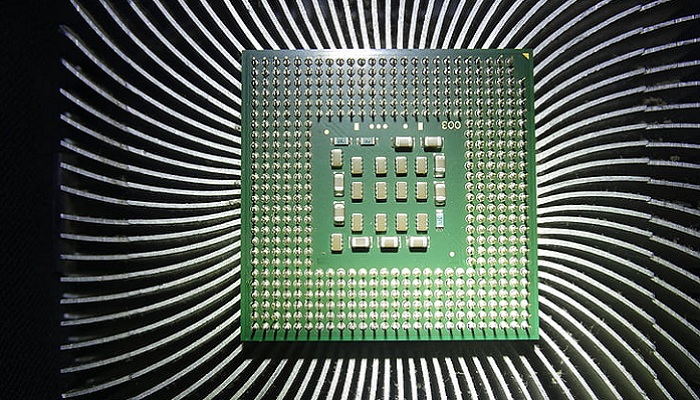

The MIPS architecture refers to the microprocessors introduced in 1985 and developed by MIPS Technologies. These processors are designed to be used in embedded systems.

Technically, these specific types of processors use a Reduced Instruction Set Computer or RISC.

There is a specialized version of MIPS processors called the MIPS-X that are also designed to be used in small embedded systems such as DVD players.

KEY TAKEAWAYS

- The MIPS architecture refers to a basic RISC instruction set architecture and the processors with such an architecture are used mainly in the embedded systems.

- Though initially the MIPS architecture was based on 32 bits, later on 64-bit versions were also developed.

- There are different versions and optional extensions of MIPS available and in use to fit into different types of embedded systems.

- In the MIPS architecture all the instructions are 32 bits, where 8 bits represent one byte, a half word and a word are represented by 2 bytes or 16 bits and 4 bytes or 32 bits, respectively.

- Each character in this architecture needs 1 byte and an integer 4 bytes of storage, numbers are signified by literals such as 2, characters are enclosed in single quotes like ‘c’ and the strings in double quotes like ‘Minecraft.’

Understanding MIPS Architecture

MIPS is a particular kind of Microprocessor without Interlocked Pipeline Stages, which is also the full form of it.

Though this is not commonly known among the general public, it is very common in the engineering fields.

Typically, this is a load/store architecture, which is also referred to as a register-register architecture, with the exception of the load/store instructions used to access the memory and all instructions typically function on the registers.

The good thing about the MIPS processor architecture is that a lot of complicated functions are removed.

This, in turn, helps in enhancing the raw processing power of the CPU.

The fundamental idea of developing the MIPS architecture is to increase the operational speed of the Central Processing Unit without it being interrupted by the additional functionalities.

Therefore, it is not surprising that the microprocessors with MIPS architecture have so fast whittled down to the basics.

Several manufacturers of embedded systems realized that these specific types of chips could be used in their systems very easily with very little or no modification required for it.

The MIPS architectures earlier came only in 32-bit version, but, later on, 64-bit versions were also developed.

You will find different versions of it with diverse features and capabilities available, along with a few other optional, application-specific extensions as well.

The different versions of the MIPS architecture are:

- MIPS I – This is a load/store architecture thirty-two General Purpose Registers or GPRs with 32 bits.

- MIPS II – This has a large number of instruction sets added and the load delay slot removed.

- MIPS III – This is backwards-compatible and provides additional support for 64-bit memory addressing as well as integer operations.

- MIPS IV – This is the superset of MIPS III that is compatible with all of the versions of MIPS. It was developed mainly with the intention of enhancing the floating point performance.

- MIPS V – This version comes with an additional data type called the Paired Single or PS as well as variants of existing FP instructions, compare and conditional move, and new instructions.

- MIPS 32 – This architecture is based on MIPS II and comes with prefetch instructions, conditional moves, multiply-add instructions, cache control instructions, and other features included in it.

- MIPS 64 – This architecture adds a MIPS 32 mode to run a code in 32 bits code and also comes with MUL and MADD instructions, cache control instructions and more.

- microMIPS – The microMIPS architecture is available in two variants microMIPS32 and microMIPS64. These are the MIPS 32 and MIPS 64 architectures, respectively.

There are also a few other Application Specific Extensions available that are based on the MIPS 32 and MIPS 64 architectures and are collectively called the ASEs.

These ASEs come with features that enhance the performance and efficiency of the processors while handling specific types of workloads, such as digital signal processing, for example.

Some of the ASEs are:

MIPS MCU – These ASEs are developed for microcontroller applications with additional support for the interrupt controller. It enhances I/O peripheral control functions and reduces the interrupt latency, two major requirements of a microcontroller system design.

MIPS16 – These ASEs are extensions for MIPS I to V and reduce the size of the application by as much as 40% since they use 16-bit instead of 32-bit instructions.

They also enhance the hit rate of the instruction cache and power efficiency offering a performance that is equivalent to the base architecture.

MIPS Digital Signal Processing (DSP) – These ASEs come with newer instruction sets that help in expediting a wide range of media applications, especially those related to audio and video.

With a state in the integer pipeline, the DSP module needs negligible additional logic for the MIPS processor cores to function.

MIPS SIMD architecture (MSA) – These ASEs also come with several instruction sets and features that accelerate multimedia.

MIPS virtualization – This ASE supports virtualization technology with appropriate hardware.

MIPS multi-threading – This ASE enhances the performance of those applications that need more fine-grained thread processing. Each core in it can support as many as two Virtual Processing Elements or VPEs sharing a single pipeline and other hardware resources.

They also allow allocating processor cycles to the threads and sets the priorities of the relative threads with a discretionary QoS or Quality of Service manager block.

SmartMIPS – This ASE is supported only by MIPS 32 and improves the performance of the processor and at the same time reduces consumption of memory for smart card software.

MIPS Digital Media eXtension (MDMX) – Just as the name implies, this ASE accelerates multimedia applications common in the RISC and CISC systems.

MIPS-3D – This ASE improves the performance of the applications that involve 3D graphics with the additional instructions.

Where is MIPS Used?

Though the MIPS chips were used extensively in the personal desktop computers, workstation, and server computers in the 1980s, these basic RISC systems found a prominent place in the embedded systems later on.

Apart from that, the features of this specific type of architecture and the design of the MIPS chips allow them to be used in the embedded systems that come with small computers built in them.

It helps them to run more sophisticated devices and gadgets such as:

- Telephones

- Video gaming consoles

- Car computer systems

- Set-top boxes

- Wireless routers

- Residential gateways

- LTE modems

- Microcontrollers

- Different Open Virtual Platforms or OVPs as simulators or emulators.

The most significant reason that the MIPS came to an unexpected and sudden halt and moved into the embedded systems is the announcement of Microsoft that their operating system would not support a large range of RISC chips any more.

However, other operating systems continued to support RISC chips, which is why the MIPS migrated to embedded systems.

Is MIPS a Programming Language?

Literally, the term MIPS is an architecture and an acronym for Microprocessor without Interlocked Pipeline Stages but, technically, it also refers to the assembly language of the processor.

However, this language needs a deeper understanding of the operation of the systems at a lower level before creating MIPS assembly language code.

It needs a very good IDE or Integrated Development Environment. This will help in compiling and executing the MIPS assembly language code.

The general structure of a typical program created in MIPS assembly language has two basic parts such as:

- The data declaration section

- The code section.

Data declaration section:

This is the section where the variables are created and defined that are to be used in the program. This is also the section where storage is assigned to the Random Access Memory or RAM.

The different variables declared by the MIPS assembly language program are:

- The “name” – This signifies the name of the created variable.

- The “storage_type” – This signifies the type of data to be stored.

- The “value(s)” – This signifies the type of information to be stored.

Code section:

This is where the instructions are written that are to be carried out by the program. The code section has a starting point and an ending point marked with the labels “main” and “exit” system call.

This specific section involves two specific functions, namely the manipulation of registers and the performance of arithmetic operations.

In the manipulation of registers, there are three basic concepts utilized such as:

- Load addressing – Here the RAM address of a variable is copied and stored in the temporary register.

- Indirect addressing – Here the value stored in the RAM address is copied into the temporary register.

- Indexed addressing – Here the RAM address of the register is offset by a particular value to get the value stored in the address of another RAM.

Performance of arithmetic operations:

There are three operands used in most arithmetic operations in the MIPS assembly language and all of these are registers and their size is a word.

The general format of the arithmetic operations in this language are:

- The “arithmetic_operation” or the operation that is being performed

- The “storage_register” which is used to store the result of the arithmetic calculation

- The “first_operand” which refers to the register containing the first operand of the arithmetic operation

- The “second_operand” which refers to the register containing the second operand of the operation.

The most common arithmetic operations in the MIPS assembly language are:

- Addition, which is represented as “add”

- Subtraction, which is represented as “sub”

- Multiplication, which is represented as “mult” and

- Division which is represented as “div.”

Is MIPS Better Than X86?

Though x86 is a bit more straightforward and offers better register usage, there is nothing to whine about it.

In fact, considering its other features, MIPS is certainly better than x86 in spite of the fact that it is more popular and there are a lot of online resources available.

The main reasons for the MIPS architecture to have a slight edge over the x86 architecture are:

- x86 comes with more complex instructions as compared to the MIPS architecture

- The instruction set is not very symmetric due to its strong backward compatibility

- The complex instruction sets are pretty slow to run on newer systems

- The instruction sets also do not offer any significant benefit

- It has a very limited set of registers available

- It is very difficult to generate binary in x86 due to the variable length of the instructions and multiple addressing modes.

Do Modern Computers Use MIPS?

Yes, modern computers still use MIPS processors, especially in smaller computing devices such as routers, modems and others, apart from the smaller home computing systems.

The proof that the MIPS is still used today is the fact that newer versions of processors based on this specific architecture are being designed and launched.

Several companies still use the MIPS architecture in designing their modern low-cost microcontrollers that are targeted for the consumer products and supercomputers.

What are the Characteristics of MIPS?

The most significant characteristic of the MIPS architecture is its larger number of registers. Also, it is able to deliver higher performance per square millimeter for the IP cores and higher levels of power efficiency for the System on Chip or SoC design.

Some other notable characteristics of the Microprocessor without Interlocked Pipeline Stages architecture are:

- The character and the number of the instructions

- The perceptible pipeline delay slots

- The most competent and true RISC architecture

- Architectural sophistication

- Industry-leading and widespread product portfolio

- A well-defined roadmap

- True 32-bit and 64-bit binary similarity from low-end to high-end

- An increasingly open operating system

- App portability

- Sturdy and substantial setup of the base ecosystem

All these attributes have helped the MIPS architecture to bring a proper balance between performance and cost making it a reliable choice for the CPU users.

Is MIPS a RISC or CISC?

Typically, the MIPS is a RISC or Reduced Instruction Set Computer processor architecture that supports much simpler and fewer instructions as compared to the CISC counterparts.

Conforming to the RISC architecture, the MIPS architecture is much faster at completing the instruction cycles as compared to the CISC architecture.

The main reason for this is its simpler design and, as said earlier, its fewer instruction sets.

Just as the RISC processors are more efficient these days, the MIPS architecture is also equally efficient, giving it that significant edge over the CISC processors.

Moreover, it is normally accepted that even the most popular CISC processors that are available, such as the Intel Pentium, translate the CISC instructions internally into RISC instructions before they are carried out.

In addition to that, another good reason to say that the MIPS architecture conforms to the RISC processor architecture is that they both characteristically have a load-store architecture design.

This means that there are generally two instructions for accessing the memory. These are:

- A load or l instruction that loads the data from the memory

- A store of S instruction that writes the data to the memory.

Apart from that, it also means that the memory cannot be accessed directly by any of the other instructions.

Technically, this signifies that, if there is an instruction given such as “add this byte from memory to register 1,” in the case of a CISC instruction set, it will essentially need two specific instructions of load and store in a load-store architecture.

These two specific types of instructions would be as follows:

- Load this byte from memory into register 2 and

- Add register 2 to register 1.

Another significant difference between the CISC processor architecture and the RISC processor architecture, and also subsequently the MIPS processor architecture, is that the CISC architecture offers several different addressing modes.

On the contrary, the MIPS processor architecture only allows for a single and simple addressing mode.

In order to spell out an address, you will need to specify both a register as well as a constant.

Ideally, in the RISC and MIPS architectures, you will need four instructions rather than one as well as an additional register, r4.

The same can be done with only a single instruction is typically CISC architecture.

However, in spite of all these requirements, the internal circuitry of the Reduced Instruction Set Computer processor architecture is much simpler, just as that of the MIPS processor architecture. That is why it can be made very fast.

However, how this can be made is a completely different topic and beyond the scope of this article.

MIPS vs ARM

- The MIPS architecture is supposed to be cleaner and simpler, but, in comparison, the ARM is considered to be more complex in design and architecture.

- The MIPS architecture conforms to the RISC processor architecture, but, in comparison, the ARM is more like the CISC processor architecture.

- There are fewer instruction sets in the MIPS processor architecture as there are in the RISC processor architecture, but, on the other hand, ARM characteristically comes with so many additional instructions that it resembles a CISC processor architecture.

- There are a lot fewer addressing modes in the MIPS processor architecture as compared to the ARM. It includes register, immediate, Program Counter relative, pseudo-direct, and base addressing modes as opposed to immediate, register, scaled, pre-indexed, post-indexed, pre-indexed with write back, and program counter relative addressing modes of the ARM.

- The MIPS processor architecture offers a much higher performance thereby bringing a much more competitive price/performance ratio to the table, which the ARM is unable to offer.

- The 64-bit capabilities of the MIPS processor architecture also make it notably different from the ARM.

- The ARM, however, offers a much better and higher power/performance ratio with a more flexible set of options and memory serves in constructing cores, while the MIPS processor architecture is unable to offer such benefits.

- In spite of having the same and a fixed instruction size of the instruction sets in both, the MIPS architecture classically has 32 registers while the ARM has only half of them.

- The output and power efficiency of the MIPS processor architecture are not as high as those of the ARM because the processors do not support 64-bit data buses between the caches and the core as the ARM processors do.

- More efficient context switching is allowed by the MIPS processor architecture due to its support for the execution of several banks of registers. This is, however, not offered by ARM.

- The MIPS processor architecture offers two distinct registers for holding the results of multiply operations, but, in comparison, ARM offers only General Purpose Registers for executing arithmetic operations as well as all the other functions.

- There is no equivalent instruction in the MIPS processor architecture as compared with the ARM MOV instruction.

- The ADD instruction in the MIPS processors usually produces an exception on the overflow and therefore it is used rarely in comparison to ARM.

- For the sake of comparison, all data processing instructions in the MIPS processor offer the SLT or System Level Test but all ARM sets the codes for ALU operations by default.

- The load word and store word for the MIPS processors are represented as ‘lw’ and ‘sw’, but, in comparison, in the ARM the load and store words are ‘LDR’ and ‘STR.’

- The syntax used in MIPS typically is $0-$31 or $v0, but, in comparison, ARM uses r and a number ranging from r0-rn.

- The MIPS processors are typically used for market applications, embedded systems and networking because of their RISC nature but, in comparison, the ARM is used for more technical applications particularly in the consumer electronic devices such as tablets, mobile phones, and multimedia players.

- There are only two operating modes in the MIPS, namely, the kernel mode and the user mode. On the other hand, ARM has a lot more operating modes such as user mode, system mode, supervisor mode, abort mode, undefined mode, interrupt mode, and fast interrupt mode.

- Conditional execution in MIPS needs building a control structure along with a branch statement for creating conditional processing and loops, but, in comparison, in the ARM architecture the condition field in the instructions specifies whether or not the processor would execute those instructions.

- For stack implementation, MIPS architecture follows the traditional method where the stack spreads out down in the memory. On the other hand, the ARM architecture supports both ascending as well as descending stack implementation.

Conclusion

As you can see from this article, the Microprocessor without Interlocked Pipeline Stages architecture is quite useful in increasing the raw processing power of a CPU.

Add to that, being a simpler architecture, it is quite efficient as compared to the CISC processors, which is why different variants of it are so popular.